MIT-Ingenieure bauen fortschrittliche Mikroprozessoren aus Kohlenstoff-Nanoröhrchen.

Der neue Ansatz nutzt die gleichen Fertigungsprozesse wie bei Siliziumchips und bietet entscheidende Fortschritte in der Entwicklung von Computern der nächsten Generation.

Nach Jahren der Bewältigung zahlreicher Entwicklungs- und Fertigungsherausforderungen haben die Forscher des MIT einen modernen Mikroprozessor aus Kohlenstoff-Nanoröhrchen-Transistoren entwickelt, die allgemein als schnellere, umweltfreundlichere Alternative zu ihren traditionellen Silizium-Pendants angesehen werden.

Der Mikroprozessor, der heute in der Zeitschrift Nature beschrieben wird, kann mit herkömmlichen Verfahren zur Herstellung von Siliziumchips hergestellt werden und stellt einen wichtigen Schritt in Richtung einer praktischeren Anwendung von Mikroprozessoren mit Kohlenstoff-Nanoröhren dar.

Siliziumtransistoren – kritische Mikroprozessorkomponenten, die zur Durchführung von Berechnungen zwischen 1 und 0 Bit wechseln – sind seit Jahrzehnten in der Computerindustrie etabliert. Wie vom Moore’s Law vorhergesagt, war die Industrie in der Lage, alle paar Jahre die Transistoren zu verkleinern und mehr Chips für die Durchführung immer komplexerer Berechnungen zu platzieren. Doch Experten prognostizieren heute eine Zeit, in der Siliziumtransistoren nicht mehr schrumpfen und immer uneffektiver werden.

Die Herstellung von Feldeffekttransistoren (CNFET) aus Kohlenstoff-Nanoröhren ist zu einem wichtigen Ziel für den Bau von Computern der nächsten Generation geworden. Die Forschung zeigt, dass CNFETs Eigenschaften haben, die eine etwa 10-fache Energieeffizienz und weitaus höhere Geschwindigkeiten im Vergleich zu Silizium versprechen. Aber wenn die Transistoren im kleinen Maßstab hergestellt werden, weisen sie oft viele Mängel auf, die die Leistung beeinträchtigen, so dass sie nicht praxistauglich sind.

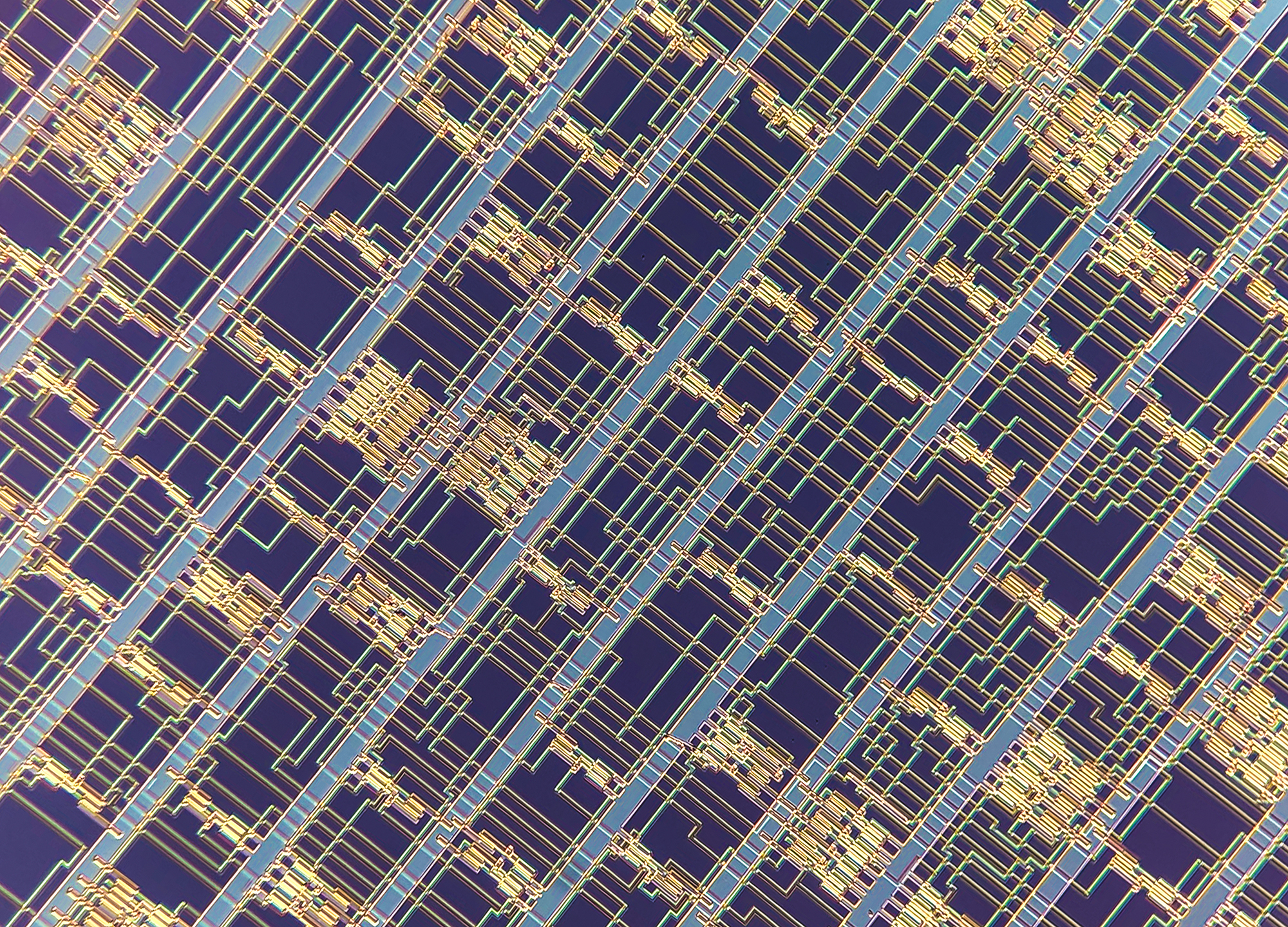

Eine Nahaufnahme eines modernen Mikroprozessors, der aus Carbon Nanotube Field Effect Transistoren besteht. Danksagungen – Bild: Felice Frankel, MIT

Die MIT-Forscher haben neue Techniken entwickelt, um Mängel drastisch zu reduzieren und eine vollständige Kontrolle der Funktion bei der Herstellung von CNFETs unter Verwendung von Prozessen in den herkömmlichen Siliziumchip-Gießereien zu ermöglichen. Sie zeigten einen 16-Bit-Mikroprozessor mit mehr als 14.000 CNFETs, der die gleichen Aufgaben wie kommerzielle Mikroprozessoren erfüllt. Das Nature Paper beschreibt das Design des Mikroprozessors und umfasst mehr als 70 Seiten, auf denen die Herstellungsmethode beschrieben wird.

Der Mikroprozessor basiert auf der Open-Source-Chip-Architektur RISC-V, die eine Reihe von Instruktionen enthält, die ein Mikroprozessor ausführen kann. Der Mikroprozessor der Forscher war in der Lage, den gesamten Befehlssatz präzise auszuführen. Es wurde auch eine modifizierte Version des klassischen Programms „Hello, World!“ ausgeführt, das ausgedruckt wurde, „Hello, World! Ich bin RV16XNano, hergestellt aus CNTs.“

„Dies ist bei weitem der fortschrittlichste Chip aus einer noch jungen Nanotechnologie, die für ein leistungsstarkes und energieeffizientes Computing vielversprechend ist“, sagt Co-Autor Max M. Shulaker, der Emanuel E Landsman Career Development Assistant Professor für Elektrotechnik und Informatik (EECS) und Mitglied der Microsystems Technology Laboratories. „Es gibt Grenzen für Silizium. Wenn wir weiterhin Fortschritte bei der Datenverarbeitung erzielen wollen, stellen Kohlenstoff-Nanoröhrchen einen der vielversprechendsten Wege dar, um diese Grenzen zu überschreiten.

Zusammen mit Shulaker arbeiten folgende Personen an dem Projekt: Erstautor und Postdoc Gage Hills, Doktoranden Christian Lau, Andrew Wright, Mindy D. Bischof, Tathagata Srimani, Pritpal Kanhaiya, Rebecca Ho und Aya Amer, alle von EECS; Arvind, der Johnson Professor für Informatik und Ingenieurwesen und Forscher im Labor für Informatik und künstliche Intelligenz; Anantha Chandrakasan, der Dekan der Ingenieurschule und der Vannevar Bush Professor für Elektrotechnik und Informatik; und Samuel Fuller, Yosi Stein und Denis Murphy, alle analoge Geräte.

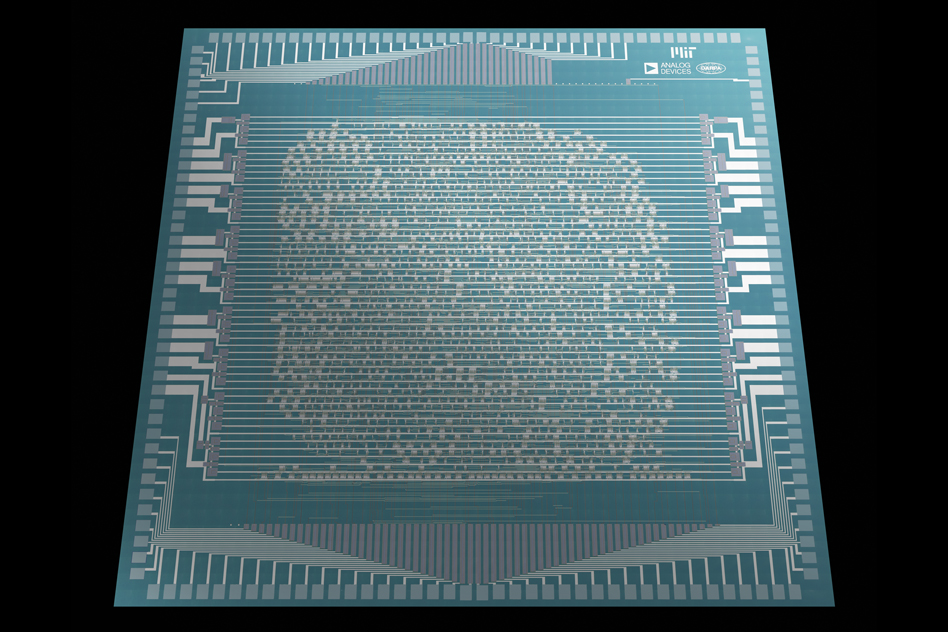

Die Ingenieure des MIT haben einen modernen Mikroprozessor aus Carbon Nanotube Field Effect Transistoren (im Bild) gebaut, die als schneller und umweltverträglicher als Siliziumtransistoren gelten. Der neue Ansatz verwendet die gleichen Herstellungsverfahren wie bei Siliziumchips. Danksagungen – Bild: Felice Frankel, MIT

Bekämpfung des „Fluchs“ von CNFETs

Der Mikroprozessor baut auf einer früheren Simulation auf, die von Shulaker und anderen Forschern vor sechs Jahren entwickelt wurde und die nur 178 CNFETs hatte und mit einem einzigen Bit an Daten lief. Seitdem haben Shulaker und seine MIT-Kollegen drei spezifische Fragestellungen bei der Herstellung der Geräte angegangen: Materialfehler, Fertigungsfehler und Funktionsprobleme. Hills übernahm den Großteil des Mikroprozessorentwurfs, während Lau den größten Teil der Fertigung übernahm.

Seit Jahren ist der Fehler, der den Kohlenstoff-Nanoröhren innewohnt, ein „Fluch des Feldes“, sagt Shulaker. Im Idealfall benötigen CNFETs halbleitende Eigenschaften, um ihre Leitfähigkeit entsprechend den Bits 1 und 0 ein- und auszuschalten, aber unvermeidlich ist, dass ein kleiner Teil der Kohlenstoff-Nanoröhrchen metallisch ist und den Transistor verlangsamt oder stoppt. Um gegenüber diesen Ausfällen widerstandsfähig zu sein, benötigen moderne Schaltungen Kohlenstoff-Nanoröhrchen mit einer Reinheit von etwa 99,999999 Prozent, was heute praktisch nicht mehr herstellbar ist.

Die Forscher entwickelten eine Technik namens DREAM (Akronym für „Design Resiliency against Metallic CNTs“), die metallische CNFETs so positioniert, dass sie die Datenverarbeitung nicht stören. Damit lockerten sie diese strengen Reinheitsanforderungen um etwa vier Größenordnungen – oder 10.000 mal -, was bedeutet, dass sie nur Kohlenstoff-Nanoröhrchen mit einer Reinheit von etwa 99,99 Prozent benötigen, was derzeit möglich ist.

Das Entwickeln von Schaltungen erfordert im Grunde genommen eine Auswahl an verschiedenen Logikgattern, die an Transistoren angeschlossen sind, die kombiniert werden können, um beispielsweise Addierer und Multiplikatoren zu erzeugen – wie das Kombinieren von Buchstaben im Alphabet, um Wörter zu erzeugen. Die Forscher stellten fest, dass die metallischen Kohlenstoff-Nanoröhrchen verschiedene Paarungen dieser Gates unterschiedlich beeinflussen. Ein einzelnes metallisches Kohlenstoff-Nanoröhrchen in Gate A kann beispielsweise die Verbindung zwischen A und B unterbrechen. Mehrere metallische Kohlenstoff-Nanoröhrchen in Gate B können jedoch keine ihrer Verbindungen beeinträchtigen.

Im Chipdesign gibt es viele Möglichkeiten, Code auf eine Schaltung zu implementieren. Die Forscher führten Simulationen durch, um all die verschiedenen Gate-Kombinationen zu finden, die widerstandsfähig und nicht widerstandsfähig gegenüber metallischen Kohlenstoff-Nanoröhren sind. Anschließend passten sie ein Chip-Design-Programm an, um automatisch die Kombinationen zu ermitteln, die am wenigsten von metallischen Kohlenstoff-Nanoröhren betroffen ist. Beim Entwurf eines neuen Chips verwendet das Programm nur die robusten Kombinationen und ignoriert die anfälligen Kombinationen.

„Das Wortspiel’Träumen‘ ist durchaus beabsichtigt, denn es ist die Traumlösung“, sagt Shulaker. „Das ermöglicht es uns, Kohlenstoff-Nanoröhrchen von der Stange zu kaufen, diese auf einen Wafer zu werfen und unsere Schaltung einfach wie gewohnt aufzubauen, ohne etwas anderes zu tun.“

Peeling und Tuning

Die CNFET-Fertigung beginnt mit dem Aufbringen von Carbon Nanotubes in einer Lösung auf einen Wafer mit vorgefertigten Transistorarchitekturen. Einige Kohlenstoff-Nanoröhrchen kleben jedoch zwangsläufig zufällig zusammen, um große Stapel zu bilden – wie Spaghetti-Stränge, die zu kleinen Kugeln geformt werden – die eine große Partikelkontamination auf dem Chip bilden.

Um diese Kontamination zu beseitigen, schufen die Forscher RINSE (für die „Entfernung inkubierter Nanoröhrchen durch selektive Exfoliation“). Der Wafer wird mit einem Präparat vorbehandelt, das die Haftung von Kohlenstoff-Nanoröhrchen fördert. Anschließend wird der Wafer mit einem bestimmten Polymer beschichtet und in ein spezielles Lösungsmittel getaucht. Das spült das Polymer weg, das nur die großen Bündel wegträgt, während die einzelnen Kohlenstoff-Nanoröhrchen am Wafer haften bleiben. Die Technik führt zu einer etwa 250-fachen Reduzierung der Partikeldichte auf dem Chip im Vergleich zu ähnlichen Methoden.

Schließlich beschäftigten sich die Forscher mit gemeinsamen funktionellen Problemen mit CNFETs. Beim Binärrechnen werden zwei Arten von Transistoren benötigt: „N“-Typen, die mit einem 1-Bit ein und mit einem 0-Bit aus schalten, und „P“-Typen, die das Gegenteil bewirken. Traditionell war es schwierig, die beiden Typen aus Kohlenstoff-Nanoröhren herzustellen, was oft zu unterschiedlich leistungsfähigen Transistoren führte. Für diese Lösung entwickelten die Forscher eine Technik namens MIXED (für „Metal Interface Engineering crossed with electrostatic doping“), die Transistoren für Funktion und Optimierung präzise einstellt.

Bei dieser Technik binden sie bestimmte Metalle an jeden Transistor – Platin oder Titan -, wodurch sie diesen Transistor als P oder N fixieren können. Anschließend beschichten sie die CNFETs in einer Oxidverbindung durch Atomschichtabscheidung, wodurch sie die Eigenschaften der Transistoren für bestimmte Anwendungen abstimmen können. So benötigen Server beispielsweise oft Transistoren, die sehr schnell arbeiten, aber gleichzeitig Energie und Leistung in sich tragen. Wearables und medizinische Implantate hingegen können langsamere Transistoren mit geringer Leistung verwenden.

Das Hauptziel ist es, die Chips in die reale Welt zu bringen. Zu diesem Zweck haben die Forscher nun damit begonnen, ihre Fertigungstechniken in einer Siliziumchip-Gießerei umzusetzen, und zwar durch ein Programm der Defense Advanced Research Projects Agency, die die Forschung unterstützt. Obwohl niemand sagen kann, wann Chips, die vollständig aus Kohlenstoff-Nanoröhrchen hergestellt werden, in die Regale kommen, sagt Shulaker, dass es weniger als fünf Jahre dauern könnte. „Wir denken, dass es nicht mehr darum geht, ob, sondern wann“, sagt er.

Die Arbeit wurde auch von Analog Devices, der National Science Foundation und dem Air Force Research Laboratory unterstützt.

Artikel: MIT / ISE, Bild: Felice Frankel, MIT